# Modeling and Simulation of Low Power 1-bit CMOS Full Adder Cells

Shruti Tiwari

Research Scholar Institute of Engineering & Technology, Alwar, Rajasthan [India] Email: tiwari.ec27@gmail.com

### ABSTRACT

The optimization of virtual supply network plays an important role in MTCMOS lowpower design...In modern high performance systems-on-chips (SoCs), more than 40% of the total active mode energy can be dissipated due to the leakage currents. With more transistors integrated on-die. leakage currents will soon dominate the total energy consumption of high performance SoCs. Furthermore, leakage current is the only source of energy consumption in an idle circuit. The battery-powered portable systems such as cell phones and laptop computers tend to have long standby modes. Reducing the leakage energy consumption of the portable systems during these long idle periods is crucial for a longer battery lifetime. As the VLSI technology and supply voltage continue scaling down, leakage power has become more and more significant in the power dissipation of today's CMOS circuits. This paper proposed a design technique to reduce leakage current in one bit full adder cell. This technique uses transistor stack effect to decrease the leakage current and leakage power also. This work analyzed the leakage current and leakage power of a full adder cell by applying the proposed technique. The delay of sum and carry outputs are also analyzed for the stack technique. The supply voltage is varied from 0.5 volt to 0.8

Prof. Dwejendra Arya Associate Professor Department of E & C, Institute of Engineering & Technology, Alwar, Rajasthan Email: d\_arya2007@yahoo.co.in

*volt. We have reduced leakage current upto 38% and leakage power upto 68%.*

**Keywords:**—Low Power, Leakage Current, Full Adder, CMOS Process Technology, transistor stacking.

# **I. INTRODUCTION**

The extensive development in the field of portable systems and cellular networks has intensified the research efforts in low power microelectronics. The low-power design has become a major design consideration. The design criterion of a full adder cell is usually multi-fold. Transistor count is, of course, a primary concern which largely affects the design complexity of many function units such as multiplier and algorithmic logic unit (ALU). The limited power supply capability of present battery technology has made power consumption an important figure in portable devices<sup>[1]</sup>. The speed of the design is limited by size of the transistors, parasitic capacitance and delay in the critical path. The driving capability of a full adder is very important, because, full adders are mostly used in cascade configuration, where the output of one provides the input for other. If the full adders lack driving capability then it requires buffer. additional which consequently increases the power dissipation. In the last decade, the full adder has gone through substantial improvement in power consumption, speed and size, but at the cost of

weak driving capability and reduced voltage swing. However, reduced voltage swing has the advantage of lower power consumption [2]. There is no ideal full adder cell that can be used in all types of applications. Hence novel architectures such as CMOS, Transmission Gate (TG), Pass-Transistor Logic (PTL), Complementary Pass-transistor Logic (CPL)<sup>[3]</sup> and Gate Diffusion Input (GDI) are proposed to meet the requirements. Each design style has its own share of advantages and disadvantages. Moore's law as we know will no longer exist in a near future, and one can already see the phenomenon of reduction of clock frequency due to excessive power dissipation. The reason is very simple, physical limits of silicon, since it is not possible to shrink atoms. Therefore, new technologies that will completely or partially replace silicon are arising. According to the ITRS roadmap<sup>[1]</sup>, these technologies have a high level of density and are slow, or the opposite: can achieve high speeds but with a huge area overhead even when comparing to future CMOS technology. Hence, traditional systems will suffer from the same problems that embedded systems suffer today: the necessity of increasing performance with power severe area and constraints. Additionally, traditional high performance architectures as the diffused superscalar machine are also achieving their limits, and recent increases in performance occurred mainly thanks to boosts in clock frequency. As an example, the clock frequency of Intel's Pentium 4 processor only increased from 3.06 to 3.2 GHz between 2002 and 2003<sup>[2]</sup>. This way, the frequency increase rate reduction, together with the foreseen slow technologies are new architectural challenges to be dealt with. In most VLSI applications, arithmetic operations play an important role. Commonly used operations are addition, subtraction, multiplication and accumulation, and the 1- bit Full Adder (FA) cell is the building block for most implementations of these operations. Obviously, enhancing the building block performance is critical for enhancing overall

system performance <sup>[3]-[6]</sup>. The vast use of this operation in arithmetic functions attracts many researchers to this field. In recent years several variants of different logic styles have been proposed to implement 1-bit adder cells <sup>[6]-[23]</sup>. They commonly aimed to reduce power consumption and increase speed. With the increasing demand for battery-operated portable applications such as cell phones, PDAs and laptop computers, as well as lowintensity applications such as distributed sensor networks, the need for power sensitive design has grown significantly. It has been shown that reducing the supply voltage is the most direct means of reducing dissipated power <sup>[5], [6],</sup> and operating CMOS devices in the subthreshold region is considered to be the most energyefficient solution for low-performance applications<sup>[5]</sup>.

Designing low-power VLSI systems has become an important performance aim because of the fast growing technology in mobile computation and communication field <sup>[24], [25]</sup>. There is one basic approach to reduce power consumption of circuits in scaled technologies. One approach is reducing the dynamic power consumption during the active mode operation of the device and the other is the reduction of leakage current during the standby mode<sup>[26]</sup>. The power consumption of a CMOS digital circuit can be expressed as in equation (1) and equation (2).

Where f is the clock frequency, C is the average switched capacitance per clock cycle, Vdd is the supply voltage,  $I_{short}$  is the short circuit current and  $I_{leak}$  is the off current. Supply voltage reduction is a widely accepted methodology for reducing dynamic power, but it has an adverse effect on circuit performance. To maintain high performance, the threshold voltage  $V_t$  must also be scaled down that causes an exponential increase in the sub-

threshold leakage<sup>[27]</sup>. Static power dissipation is the power dissipated by the circuit when it is in sleep mode or standby mode. Average leakage power is given by equation (3).

$$Pleak = \frac{1}{T \int Ileak * Vdd}$$

.....(3)

Where  $I_{leak}$  is the leakage current that flows in a transistor when it is in off state. This static power dominates dynamic power especially in deep sub micron circuits and also in circuits that remains in idle mode for a long time like cell phones.

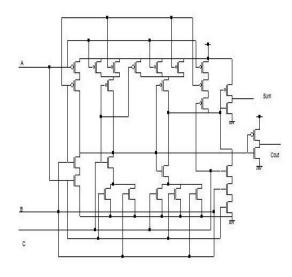

The adder is one of the most critical components of a processor, as it is used in the arithmetic logic unit (ALU), in the floatingpoint unit, and for address generation in case of cache or memory access. A one bit full adder cell is the most important and basic block of an arithmetic unit of a system. Obviously, improving its performance and decreasing its power directly leads to low power and high performance of the whole system. Therefore in this paper the focus is on the reduction of leakage current consumption of 28 transistor (28T) full adder cell which is very high in submicron technology. The rest of the paper is organized as follows. Section 2 presents the operation of 1 bit full adder section 3 presents proposed leakage reduction techniques. Section 4 presents the simulation results of the full adder with and without the leakage reduction technique and section 5 gives the conclusion.

# **II. WORKING OF 1 BIT FULL ADDER**

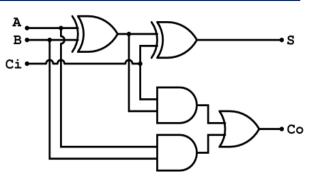

A Full Adder (FA) is a logical circuit that performs an addition operation on three binary digits. The full adder produces a sum and a carry value, which are both binary digits. The logical diagram of full adder is shown in figure 1.

Figure 1 : Logic Diagram of full adder

A FA adds binary numbers and accounts for values carried in as well as out. A one-bit full adder adds three one-bit numbers, often written as A, B, and Ci here A, B are the operands, and Ci is a bit carried in (in theory from a past addition by [32]). The circuit produces a twobit output sum typically represented by the signals Co (Carry) and S (Sum). The Boolean equation and truth table are shown bellow.

# S= A XOR B XOR C.....(4) C0= (A AND B) OR (B AND Ci) OR (Ci AND A).....(5)

Table 1: Truth Table for Full Adder

| Α | В | Ci | Sum<br>(S) | Carry<br>(C0) |

|---|---|----|------------|---------------|

| 0 | 0 | 0  | 0          | 0             |

| 0 | 0 | 1  | 1          | 0             |

| 0 | 1 | 0  | 1          | 0             |

| 0 | 1 | 1  | 0          | 1             |

| 1 | 0 | 0  | 1          | 0             |

| 1 | 0 | 1  | 0          | 1             |

| 1 | 1 | 0  | 0          | 1             |

| 1 | 1 | 1  | 1          | 1             |

A FA can be constructed by cascading of two HA (Half Adder). The A and B are connected to the input of first HA and the sum of first HA is connected as one input along with Ci to second HA and it give SUM output. The logical OR of first and second HAs carry

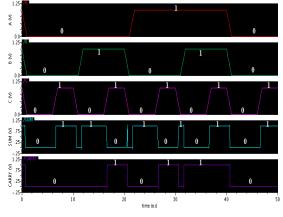

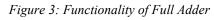

outputs a gives CARRY output of FA shown in  $^{[33]}$ . A schematic of one bit full adder is shown in figure 2. Figure 3 shows the functionality of full adder.

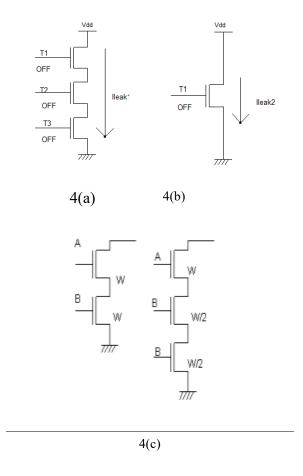

power than a single transistor that is turned OFF [Refer Figure 4 (B)]. This is because each transistor in the stack induces a slight reverse bias between the gate and source of the transistor right below it, and this increases the threshold voltage of the bottom transistor making it more resistant to leakage. Therefore in Figure 4 (A) transistor T2 leaks less current than transistor T1 and T3 leaks less than T2. Hence the total leakage current through the transistors T1,T2 and T3 is decreased as it flows from Vdd to ground node. So  $I_{leak1}$  is less than I<sub>leak2</sub><sup>[29]</sup>. If natural stacking of transistors do not exist in a circuit, then to utilize the stacking effect a single transistor of width W is replaced by two transistors each of width W/2 <sup>[30]</sup> as shown in Figure 4 (C).

Figure 4: Transistor Stacking Effect

# III. LEAKAGE CONTROL USING TRANSISTOR STACKING

The leakage current flowing through a stack of series connected transistors reduces when more than one transistor of the stack is turned OFF. This effect is known as the "Stacking Effect". When two or more transistors that are switched OFF are stacked on top of each other as shown in figure 4 (A), then they dissipate less leakage

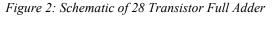

Figure 5: Circuit of a 28 transistor Full Adder with stack

#### 4. SIMULATION RESULT

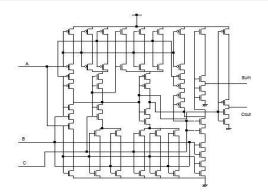

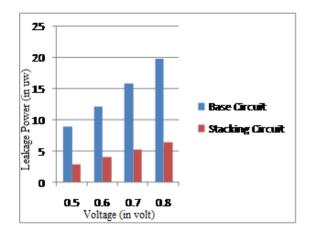

In this paper, a 28T full adder cell is implemented in 45 nm technology. Initially the leakage current of the above circuit is computed without any reduction technique (Base case). Then the proposed methods transistor stacking (Stack) is applied to the circuits. Figure 2 and Figure 5 shows the circuit of a 28T full adder cell and full adder with stack respectively. The simulations are performed on Cadence Virtuoso tool in 45 nm CMOS process technology at a temperature of 27° C by varying the supply voltage Vdd from 0.5 volt to 0.8 volt. The simulation results are shown in figure 6 and figure 7. The result shows that with the proposed method stack technique, the leakage current decreases at all supply voltages ranging from 0.5 volt to 0.8 volt and the reduction is more with the stacking method.

Figure 6: Comparison of Leakage Current between Base Circuit and Stacked Circuit

Figure 7: Comparison of Leakage Power between Base Circuit and Stacked Circuit

### 5. CONCLUSION

It can be seen that the highest speed of operation i.e. Minimum delay is achieved by circuit with low threshold MOSFET in P-net and N-net. However, it has moderate power consumption and excessively high leakage power consumption. Again, the speed of operation is lowest i.e. Maximum delay is achieved by the circuit with high threshold MOSFET in P-net and N-net. Moreover, highest average power consumption is there. However, it has very low leakage power consumption. Finally, the speed of operation is Modest i.e. intermediate delay is achieved by the circuit with high and low threshold MOSFET in Nnet and P-net respectively. Moreover, it has lowest average power consumption and very low leakage power consumption. So, it can be successfully considering concluded that all design constraints, circuit with high and low threshold MOSFET in N-net and P-net respectively. In this work the analysis of leakage current of a 28T full adder cell is carried out in 45nm CMOS process technology at different supply voltages using stacking reduction techniques. The leakage current decreases with the proposed technique and the reduction is more with stacking. So a low leakage adder for use in the arithmetic unit of a processor can be designed using the proposed methods.

9

## VI. ACKNOWLEDGEMENT

The author would like to thank Institute of Engineering & Technology, Alwar, Rajasthan for providing the Tools and Technology for the work to be completed.

# **REFERENCES:**

- [1] International Technology Roadmap for Semiconductors, 2004.

- [2] M.J Flynn, P. Hung, "Microprocessor design issues: thoughts on the road ahead". IEEE Micro, Vol. 25, Issue 3, May-June 2005 pp. 16 - 31.

- [3] J. Rabaey., A. Chandrakasan, B. Nikolic, Digital Integrated Circuits, A Design Perspective, 2nd 2002, Prentice Hall, Englewood Cliffs, NJ.

- [4] J. Uyemura, CMOS Logic Circuit Design, Kluwer, 1999, ISBN 0-7923-8452-0.

- [5] N. Weste, K. Eshragian, Principles of CMOS VLSI Design: A Systems Perspective, Addison-Wesley, 1993.

- [6] R. Zimmermann, W. Fichtner, "Lowpower logic styles: CMOS versus pass-transistor logic," IEEE J. Solid-State Circuits, Vol. 32, pp. 1079– 1090, July 1997.

- [7] H.T. Bui, A.K. Al. Sheraidah, Y. Wang., "Design and Analysis of 10transistor Full Adders Using Novel XORXNOR Gates," Technical Report, Florida Atlantic University, October 1999.

- [8] N. Zhuang, H. Ho, "A new design of the CMOS full adder," IEEE. J. of Solid-State Circuits, Vol. 27, No. 5, pp. 840- 844, May 1992.

- [9] Chandrakasan, Low Power Digital

CMOS Design, Ph.D. Thesis, University of California at Berkeley, Memorandum No. UCB/ERL M94/65, August 1994.

- [10] H.T. Bui, Y. Wang, Y. Jiang, "Design and analysis of lowpower10transistor full adders using novel XOR-XNOR gates," IEEE Transactions on Circuits & Systems II, Vol. 49, pp. 25–30, Jan. 2002.

- [11] U. Ko, P. T. Balsara, W. Lee, "Low-Power Design Techniques for High Performance CMOS Adders," IEEE Transactions on VLSI Systems, Vol. 3, No. 2, pp. 327-333, June 1995.

- [12] S. F. Hsiao, M. R. Jiang, J.S. Yeh, "Design of high-speed low-power 3-2 counter and 4-2 compressor for fast multipliers," ElectroN. Letter, Vol.34, No. 4, pp. 341–343, 1998.

- [13] D. Radhakrishnan, A.P. Preethy, "Low-power CMOS pass logic 4-2 compressor for high-speed multiplication," Proc. 43rd IEEE Midwest Symp. Circuits & Systems, Vol. 3, pp. 1296–1298, 2000.

- [14] A.M. Shams, M.A. Bayoumi, "A structured approach for designing low -power adders," Proc. 31st Asilomar Conf. Signals, Systems Computers, Vol. 1, pp. 757–761, 1997.

- [15] A.M. Shams, M.A. Bayoumi, "A novel high-performance CMOS 1-bit full-adder cell," IEEE Transactions on Circuits & Systems. II, Vol. 47, pp. 478–481, May 2000.

- [16] A.M. Shams, T.K. Darwish, M.A. Bayoumi, "Performance analysis of low-power 1-bit CMOS full adder cells," IEEE Transactions on VLSI Systems, Vol. 10, pp. 20–29, Jan.

2002.

- [17] A-Shama, M.A. Bayoumi, "A new cell for low power adders," Proc. lot. Midwest Symp. Circuits & Systems, pp. 1014-1017, 1995.

- [18] A.A. Fayed, M.A. Bayoumi, "A Low Power 10-Transistor Full Adder Cell for Embedded Architectures," Proc. IEEE Symp. Circuits & Systems, Vol. 4, pp. 226-229, Sydney, Australia, May 2001.

- [19] D. Radhakrishnan, "Low-voltage low -power CMOS full adder," Proc. Inst. Elect. Eng., Circuits Devices Systems, Vol. 148, No. 1, pp. 19–24, 2001.

- [20] O. Kavehie, K. Navi, "A Novel 54×54-bit Scalable Multiplier Architecture," 13th Iranian Conference on Electrical Engineering, pp. 367-371, May 2005.

- [21] C. Chang, J. Gu, M. Zhang, "Ultra Low-Voltage Low- Power CMOS 4-2 and 5-2 Compressors for Fast Arithmetic Circuits," IEEE Transactions on Circuits & Systems, Vol. 51, No. 10, pp. 1985-1997, Oct. 2004.

- [22] K. Navi, A. Kazeminejad, D. Etiemble, "Performance of CMOS Current Mode Full Adders", IEEE Proc. Int'l. Symp. Multiple Valued Logic, pp. 27-34, May 1994.

- Kavehie, [23] K. Navi, Ο. M. Rouholamini, A. Sahafi, S. Mehrabi, "A Novel CMOS Full Adder." 20th International Conference on VLSI 6<sup>th</sup> Design held jointly with International Conference on Embedded Systems (VLSID'07), pp. 303-307, Jan. 2007, Bangalore, India.

- [24] J. Rabaey, M. Pedram, and P.Landman, "Low Power Design Methodologies," Kluwer Academic Publishers,1995.

- [25] H. E.Neil, Weste, Kamran Eshraghian, "Principles of CMOS VLSI Design A Systems Perspective," Second Edition, Addison-Wesley, 1998.

- [26] K. Roy, S.. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage Current Mechanisms and Leakage Reduction Techniques in Deepsubmicrometer CMOS Circuits," Proc. IEEE, Vol.91, No.2, pp. 305-327, February 2003.

- [27] B. Nikolic,"Design in the Powerlimited Scaling Regime," IEEE Transactions on Electron Devices, Vol.55, No.1, January 2008.

- [28] Venkatachalam and M. Franz, "Power Reduction Techniques for Microprocessor Systems," ACM Computing Surveys, Vol. 37, No. 3, pp.195-237, September 2005.

- [29] S. Narendra, V. De, S. Borkar, Dimitri A Antonisdis and Anantha P. Chandrakasan, "Full-Chip Subthreshold Leakage Power Prediction and Reduction Techniques for Sub 0.18-μm CMOS," IEEE Journal of Solid State Circuits, Vol. 39, No.2, pp.501-510, February 2004.

- [30] L. Yu Loy, W. Zhang, Z. Hui Kong, WangLing Goh and Kiat-seg-Yeo, "Body-Boot strapped Buffer Circuit for CMOS Static Power Reduction," IEEE 2008.

- [31] J. Tschanz, S. Narendra, Y. Ye, B. Bloechel, S.Borkar, V.De, "Dynamic Sleep Transistor and Bodybias for

> Active Leakage Power Control of Microprocessors," IEEE Journal of Solid State Circuits, Vol.38, No.2, pp.1838-1845, November 2003.

- [33] K. Martin, Digital Integrated Circuit Design, Oxford University Press, New York, (2000).

- [32] J. M.Rabaey, Digital Integrated Circuits, Prentice Hall, Upper Saddle River, NJ, (1996).

\* \* \* \* \*